|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

Определение цифровых последовательностей на входах ЦАП.Стр 1 из 3Следующая ⇒

Рецензия Содержание.

1. Задание на выполнение курсовой работы.......................................................................................... 4 2.1. Определение цифровых последовательностей на входах ЦАП.................................................... 4 2.2.Синтез преобразователя кода............................................................................................................. 4 2.3. Синтез счётчика импульсов.............................................................................................................. 4 2.4. Выбор и расчет генератора тактовых импульсов........................................................................... 4 2.5. Выбор схемы ЦАП............................................................................................................................. 4 2.6. Составление полной принципиальной схемы формирователя..................................................... 4 2.7. Расчет задержки распространения сигналов и потребляемой мощности.................................... 4 3.1. Разработка алгоритма формирования заданных сигналов и определение дополнительных исходных данных для проектирования.......................................................................................... 4 3.2. Определение управляющего слова................................................................................................... 4 3.3. Определение адресов портов и синтез дешифратора адреса ППИ............................................... 4 3.4. Составление полной функциональной схемы формирователя на основе МП............................ 4 3.5. Разработка детального алгоритма работы микропроцессорной системы.................................... 4 3.6. Разработка алгоритма подпрограммы задержки............................................................................. 4 3.7. Разработка программы работы микропроцессорной системы...................................................... 4 Список литературы................................................................................................................................... 4

Задание на выполнение курсовой работы. Необходимо разработать формирователь двух сигналов периодического цифрового четырехразрядного сигнала Обобщенная структурная схема формирователя реализованного аппаратным способом на «жесткой логике» представлена на рис.1.

Устройство состоит из генератора тактовых импульсов (ГТИ), счетчика импульсов (СТ), преобразователя кодов (ПК) и цифро-аналогового преобразователя (ЦАП). Формирователь сигналов работает следующим образом: импульсы с выхода генератора с периодом следования Дополнительные входы счетчика предназначены:

Определение цифровых последовательностей на входах ЦАП. Для того, чтобы ЦАП мог формировать аналоговые напряжения необходимой величины

где Значения цифрового кода

где Второе слагаемое учитывает начальное смещение цифрового кода, так как последний является только положительным, а напряжение на выходе ЦАП может иметь различную полярность. Для заданных значений Для определения цифровых последовательностей

т.е. перевести значения цифрового кода Таким образом, таблица исходных данных будет иметь следующий вид:

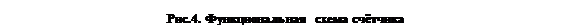

Таблица 1. Исходные данные для проектирования В соответствии с вариантом временная диаграмма напряжения на выходе ЦАП будет иметь следующий вид (рис.2): Синтез счётчика импульсов. В качестве счётчика импульсов используем интегральную микросхему К555ИЕ7. Обозначение и функциональная схема синтезируемого счетчика показана на рис.4

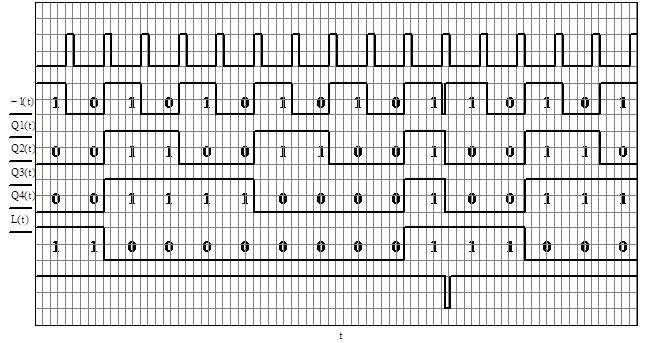

Это четырехразрядный асинхронный реверсивный счётчик с возможностью предустановки. Модуль счета счетчика 16, т.е. при работе в режиме счета он последовательно переходит из одного состояния в другое начиная с состояния 010 =00002 и заканчивая состоянием 1510 == 11112. Выводы счетчика имеют следующее назначение: Входы " D1", " D2", " D4" и " D8" предназначены для предварительной установки состояния счетчика. На эти выводы подается четырехразрядная кодовая комбинация, которую можно загрузить в счетчик. Вход " L" – вход разрешения предустановки. При подаче логического " 0" установленная на входах предустановки комбинация записывается в триггеры счетчика и появляется на выходах. Входы " +1" и " -1" - суммирующий и вычитающий входы счетчика соответственно. Срабатывание счетчика происходит при положительном перепаде напряжения на одном из входов. При этом на неиспользуемый вход должен подаваться уровень логической " 1". Вход " R" - асинхронный вход сброса всех триггеров счетчика в состояние 0. Сброс осуществляется подачей логической " I". Выходы " 1", " 2", " 4", " 8" - прямые выходы разрядов счетчика. На выходах " ≥ 15" и " ≤ 0" – формируются сигналы логического " 0" при достижении максимального и минимального состояний счетчика соответственно. Напряжение питания счетчика +5 В, потребляемый ток 34 мА. Максимальная тактовая частота 25 МГц, время установки кода счетчика около 40 нс. Исходные данные для синтеза счетчика берем из таблицы 1. Для нашего варианта счетчик должен работать в режиме вычитания, иметь 11 состояний, начальное состояние счетчика М(0)=9, конечное состояние счетчика М(10)=15. Принцип синтеза счетчиков с произвольным модулем счета заключаются в исключении из работы " лишних" состояний. Для нашего варианта требуется исключить из работы 5 " лишних" состояний, что можно осуществить с помощью принудительной установки счетчика в начальное состояние М(0)=9 вместо состояния М(10+1)=14. Такую принудительную установку можно выполнить, если на входы предустановки подать код начального состояния счетчика, а в момент перехода счетчика в состояние М(10+1) сформировать сигнал разрешения предустановки. Сигнал разрешения предустановки формируется схемой предустановки, которая по сути является дешифратором числа 14. Для синтеза схемы предустановки составим таблицу истинности ее работы, исходя из следующих предположений: логический 0, необходимый для разрешения предустановки, должен появляться на ее выходе только в момент времени, когда счетчик находится в состоянии М(10+1)=14. Это значит, что для любых других состояний счетчика на выходе схемы предустановки должна формироваться логическая 1. Таким образом, таблица истинности будет иметь вид таблицы 2.

Таблица 2. Таблица истинности схемы предустановки Записав по этой таблице логическое выражение в СКНФ, получим:

Временные диаграммы работы счетчика в этом режиме показаны на рис.5.

Согласно заданию, счетчик имеет два дополнительных входа: X1- вход установки начального состояния и Х2 - вход остановки счета. Это значит, что при подаче на входы X1 и Х2 активных логических уровней должна происходить установка начального состояния счетчика и остановка счета соответственно. Причем эти входы должны обладать наивысшим приоритетом по сравнению с другими. Поскольку установка начального состояния происходит с помощью механизма предустановки, то по сигналу X1 должен формироваться сигнал разрешения предустановки, который следует подать на вход " L" счетчика. Его формирование происходит в схеме установки начального состояния. Остановку счета можно произвести, если прекратить подачу импульсов на счетный вход счетчика по сигналу Х2. Это осуществляется в схеме остановки счета. Произведем синтез схем установки начального состояния и остановки счета. При синтезе учитываем, что для нашего варианта активными уровнями сигналов X1 и Х2 являются уровни логической " 1". Составим схему установки начального состояния счетчика, для этого составим таблицу истинности установки начального состояния счетчика.

Запишем СДНФ:

перейдя в базис ИЛИ-НЕ, получим:

Составим схему остановки счёта, для этого составим таблицу истинности остановки счёта.

Запишем СДНФ:

перейдя в базис ИЛИ-НЕ, получим:

Составим принципиальную схему счетчика импульсов, объединив элементы счетчика. Так как схема предустановки заканчивается инвертором, а в схеме установки начального состояния YПУ инвертируется, то целесообразно убрать эти два инвертора. Покажем принципиальную схему счетчика импульсов на рис.6.

Выбор схемы ЦАП.

В качестве ЦАП в проектируемом устройстве будем использовать интегральную микросхему К572ПА1. Это 10-разрядный перемножающий ЦАП, выполненный по КМОП технологии и отличающийся малой потребляемой мощностью в 0, 1 Вт. Его основные динамические характеристики: время установления выходного напряжения t У=5мкс и дифференциальная нелинейность преобразования менее 0, 8% от полной шкалы. Условное графическое обозначение ЦАП и схема его включения показана на рис.8.

Назначение выводов ИМС: Х1...Х10 - цифровые входы, причем X1 - вход младшего разряда. Uoп - вход для подключения источника опорного напряжения. Y1, Y2 - аналоговые выходы ЦАП, которые являются токовыми. Roc - вывод внутреннего резистора обратной связи. Ucc - вывод для подачи напряжения питания +5...17В. OU - вывод для подключения общего провода. Конструктивно ЦАП выполнен в 16 выводном корпусе типа DIP. В состав микросхемы входит резистивная прецизионная матрица R-2R, токовые ключи на МОП транзисторах и входные усилители-инверторы, которые обеспечивают управление ключами от стандартных уровней цифрового сигнала. Микросхема работает с прямым параллельным двоичным кодом, который подается на цифровые входы Х10...Х1 и реализует функцию перемножения опорного напряжения на цифровой код Х10...Х1 в четырех квадрантах. Благодаря тому, что коммутирующие ключи выполнены на МОП транзисторах, ЦАП допускает выбор опорного напряжения в широком диапазоне: -17...+17 В. Поскольку выходы ЦАП токовые, то для преобразования тока в напряжение к выходам Y1 и Y2 подключаются операционные усилители DA2, DA3. Операционный усилитель DA2 обеспечивает суммирование токов, поступающих с коммутирующих ключей, находящихся в состоянии " 1", a DA3 - с ключей, находящихся в состоянии " 0". В качестве операционных усилителей используем микросхему КР544УД2Г с незначительным смещением нуля и достаточно высоким быстродействием. Благодаря использованию двух операционных усилителей эта схема формирует на выходе биполярное напряжение в пределах от -Uoп до Uoп. Связь между напряжением на выходе преобразователя, опорным напряжением Uoп и цифровым кодом на входах Х10...Х1 определяется выражением:

Здесь n – количество разрядов ЦАП. В разрабатываемом устройстве, ЦАП К572ПА1 используется в восьмиразрядном включении, поэтому на два младших разряда XI и Х2 подаются постоянные логические уровни " 0". Для согласования входных уровней с выходами ТТЛ логики можно снизить напряжение питания Ucc до величины 5 В. Произведём выбор величины опорного напряжения, от которого зависит величина напряжений на выходе ЦАП. Для нашего варианта, для того, чтобы получить Umin=-7 В и Umax=7 В, значение Uоп=-7 В. Выбранное опорное напряжение подается на вывод Uоп DA1 (см. рис.8). Рассчитаем напряжение на выходе ЦАП для пяти значений цифрового кода и сведем результат в таблицу 3.

Таблица 3. Зависимость напряжений на выходе ЦАП от цифрового кода на входе при восьмиразрядном включении Список литературы 1. Методические указания к курсовой работе по дисциплине «ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА». – Самара 2000. 2. Цифровая и вычислительная техника: Учебник для вузов/ Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; под ред. Э.В. Евреинова. – М.: Радио и связь, 1991. 3. Шило В.Л. Популярные цифровые микросхемы: справочник. – М.: Металлургия, 1987.

Рецензия Содержание.

1. Задание на выполнение курсовой работы.......................................................................................... 4 2.1. Определение цифровых последовательностей на входах ЦАП.................................................... 4 2.2.Синтез преобразователя кода............................................................................................................. 4 2.3. Синтез счётчика импульсов.............................................................................................................. 4 2.4. Выбор и расчет генератора тактовых импульсов........................................................................... 4 2.5. Выбор схемы ЦАП............................................................................................................................. 4 2.6. Составление полной принципиальной схемы формирователя..................................................... 4 2.7. Расчет задержки распространения сигналов и потребляемой мощности.................................... 4 3.1. Разработка алгоритма формирования заданных сигналов и определение дополнительных исходных данных для проектирования.......................................................................................... 4 3.2. Определение управляющего слова................................................................................................... 4 3.3. Определение адресов портов и синтез дешифратора адреса ППИ............................................... 4 3.4. Составление полной функциональной схемы формирователя на основе МП............................ 4 3.5. Разработка детального алгоритма работы микропроцессорной системы.................................... 4 3.6. Разработка алгоритма подпрограммы задержки............................................................................. 4 3.7. Разработка программы работы микропроцессорной системы...................................................... 4 Список литературы................................................................................................................................... 4

Задание на выполнение курсовой работы. Необходимо разработать формирователь двух сигналов периодического цифрового четырехразрядного сигнала Обобщенная структурная схема формирователя реализованного аппаратным способом на «жесткой логике» представлена на рис.1.

Устройство состоит из генератора тактовых импульсов (ГТИ), счетчика импульсов (СТ), преобразователя кодов (ПК) и цифро-аналогового преобразователя (ЦАП). Формирователь сигналов работает следующим образом: импульсы с выхода генератора с периодом следования Дополнительные входы счетчика предназначены:

Определение цифровых последовательностей на входах ЦАП. Для того, чтобы ЦАП мог формировать аналоговые напряжения необходимой величины

где Значения цифрового кода

где Второе слагаемое учитывает начальное смещение цифрового кода, так как последний является только положительным, а напряжение на выходе ЦАП может иметь различную полярность. Для заданных значений Для определения цифровых последовательностей

т.е. перевести значения цифрового кода Таким образом, таблица исходных данных будет иметь следующий вид:

Таблица 1. Исходные данные для проектирования В соответствии с вариантом временная диаграмма напряжения на выходе ЦАП будет иметь следующий вид (рис.2): |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Последнее изменение этой страницы: 2020-02-16; Просмотров: 162; Нарушение авторского права страницы