|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

MultiSim 10.1: – быстрый стартСтр 1 из 14Следующая ⇒

MultiSim 10.1: – быстрый старт Содержание 1. Введение 2. Настройка программы MultiSim 10.1 для моделирования цифровых схем. 2.1. Главное окно программы 2.2. Установка главных преференций для проектов в Multisim 2.3. Характеристики проекта для вновь открываемой схемы. 3. Структура элементной базы Multisim 10.1. Браузер размещения компонентов. 4. Виртуальные и реальные компоненты в базе данных Multisim10.1. 5. Характеристика групп цифровых компонентов TTL - и CMOS –логики. 6. Виды цифрового моделирования в Multisim 10.1. 7. Размещение символов “земли” и источников питания. Режимы моделирования 8. Проводники и точки соединения. 9. Простейший формирователь двоичных сигналов на основе интерактивного ключа 10. Пример 1. Функционального моделирование мультиплексора MUX (2->1)) 10.1. Технология подготовки схемы 10.2. Размещение компонентов схемы MUX (2->1)) и формирователей двоичных сигналов 10.3. «Разводка» схемы и ввод пояснительных надписей 10.4. Моделированию схемы мультиплексора MUX (2->1)) 11. Формирователи и регистраторы двоичных сигналов универсального типа. 11.1. Генератор слова XWG и семисегментный индикатор 16-теричных символов DCD_Hex 11.2. Регистрация работы генератора слова XWG логическим анализатором XLA. 12. Пример 2. Функциональное моделирование комбинационной схемы 4-битного сумматора. 12.1. Синтез схемы сумматора в заданном логическом базисе 12.2. Понятие об иерархическом проектировании электронных схем. Создание подсхем. 12.2.1. Создание подсхемы полусумматора HS способом «сверху - вниз». 12.2.2. Создание подсхемы одноразрядного сумматора SM способом «снизу - вверх». 12.3. Создание схемы моделирования 4-х битного сумматора с последовательным переносом. Использование шинной организации схемы. 12.4. Проверка правил электрического проектирования схемы сумматора. 12.5. Функциональное моделирование (логическое тестирование) схемы. 12.6. Спецификация схемы сумматора. 13. Проверка правильности выполнения электрической соединений в проектах программы Multisim 10.1 14. Пример 3. Временное моделирование (или исследование времени задержки переключения JK триггера). 15. Графический самописец (дисплей) Grapher 16. Пример 4. Создание проекта моделирования канала передачи данных с контролем по mod 2. 16.1. Постановка задачи 16.2. Особенности реализации проекта в программе Multisim 10.1 16.3. Создание проекта моделирования. ■ Открытие проекта. ■ Открытие файла моделирования и отображение его в менеджере проекта. ■ Создание иерархического блока для схемы свёртки по mod 2. ■ Коррекция структуры менеджера проекта. ■ Создание схемы замещения иерархического блока. ■ Построение схемы моделирования канала передачи данных с контролем по mod 2. ■ Функциональное моделирование канала передачи данных.

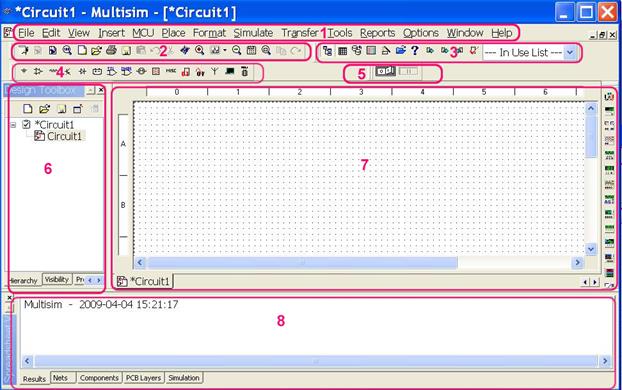

Введение Разработка любого цифрового устройства сопровождается физическим или математическим моделированием. Физическое моделирование связано с большими материальными затратами, поскольку требуется изготовление макетов и их трудоемкое исследование. Часто физическое моделирование просто невозможно из-за чрезвычайной сложности устройства, например, при разработке больших и сверхбольших интегральных микросхем. В этом случае прибегают к математическому моделированию с использованием компьютерных программ. В настоящее время разработано много подобных программ, использующих в качестве системного ядра программу SPICE -Simulation Program for Integrated Circuits Emphases (программа моделирования с ориентацией на интегральные схемы - разработка учёных университета Беркли, США), либо модели цифровых устройств на основе языков HDL (Hardware Description Languages) низкого (Altera HDL) и высокого уровней (VHDL –Very high speed integrated circuits HDL). Составленные на входном языке Spice, математические модели компонентов схемотехнических устройств с высокой степенью достоверности соответствуют реальным элементам и используются в ряде подобных программ моделирования, так, например, HSpice (фирма MetaSoftware), PSpice (фирма MicroSim), Dr.Spice и ViewSpice (фирма Deutsch Research), Micro-Cap (фирма Spectrum Software), Spice3F5 и XSpice (фирмы National Instruments, сегодняшнего собственника программного продукта MultiSim 10.1). MultiSim 10.1 представляет пакет программ для моделирования электронных схем и, при необходимости, последующей разводки печатных плат. Наследник знаменитого (особенно в академической среде) Electronics Workbench 5.12 от того же разработчика. Новые версии продуктов дополнены новыми средствами профессиональной разработки, в том числе инструментами моделирования, расширенной и улучшенной базой элементов, а также средствами совместной работы над проектом. Пользователь программы MultiSim не должен быть экспертом по программам SPICE, так как пользуется интуитивно понятной средой имитационного моделирования, гарантирующего высокое качество имитаций. 2. Настройка программы MultiSim 10.1 для моделирования цифровых схем. Главное окно программы Запустив программу и дождавшись её полной загрузки, вы увидите окно, отображённое на рис 1 (здесь красным цветом выделены главные части окна): 1. Главное меню программы (содержит команды для всех функций программы). 2. Стандартная панель, включающая общеупотребительные иконки в прикладных Windows-программах (View/Toolbars/Standard). 3. Панель управления Main (View/Toolbars/Main). Данная панель содержит кнопки для общих (основных) функций программы Multisim, а также окно In Use List, в котором содержится список всех компонентов, используемых в проекте. 4. Панель библиотек компонентов(View/Toolbars/Components). 5. Ключ симуляции (View/Toolbars/Simulation Switch), реализующий все режимы моделирования. 6. Панель (менеджер) проекта (View/Design Toolbox). Показывает иерархическую структуру схем и проектов. 7. Рабочая область ввода схемы (*Circuit) для симуляции вместе с панелью приборов (Instruments), использующихся как для задания входных сигналов, так и визуализации результатов симуляции. 8. Электронная таблица просмотра (Spreadsheet View) и редактирования параметров схемных компонентов и их обозначений (RefDes), а также просмотра результатов моделирования

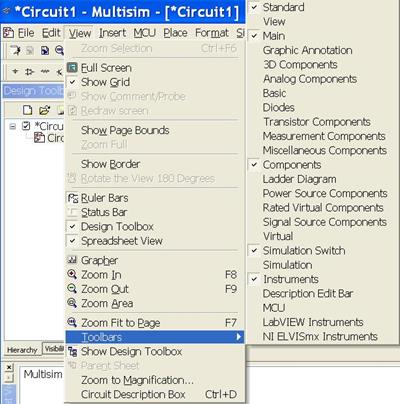

Рис. 1. Окно программы MultiSim 10.1 Для того, чтобы окно программы выглядело как на рис. 1, выполните команду меню View/Toolbars и установите опции, указанные на рис. 2.

Рис. 2. Опции команды View/Toolbars, определяющие вид окна программы Multisim 10.1 на рис.1. Footprint:

Package type: NO14 Package manufacturer: IPC-2221A/2222 Pin Count: 14 Pins information: Logical Physical Section Type ERC Status Pin Swap Group Gate Swap Group 1A 1 GRP:A D:INPUT:TTL_RCV INCLUDE A A 1B 2 GRP:A D:INPUT:TTL_RCV INCLUDE A A 1Y 3 GRP:A D:OUTPUT:TTL_DRV INCLUDE B A 2A 4 GRP:B D:INPUT:TTL_RCV INCLUDE A A 2B 5 GRP:B D:INPUT:TTL_RCV INCLUDE A A 2Y 6 GRP:B D:OUTPUT:TTL_DRV INCLUDE B A GND 7 PWR:V0 D:GND INCLUDE 3Y 8 GRP:C D:OUTPUT:TTL_DRV INCLUDE B A 3A 9 GRP:C D:INPUT:TTL_RCV INCLUDE A A 3B 10 GRP:C D:INPUT:TTL_RCV INCLUDE A A 4Y 11 GRP:D D:OUTPUT:TTL_DRV INCLUDE B A 4A 12 GRP:D D:INPUT:TTL_RCV INCLUDE A A 4B 13 GRP:D D:INPUT:TTL_RCV INCLUDE A A VCC 14 PWR:V1 D:VCC INCLUDE

■ Виртуальный компонент NAND2 ################# Component Detail Report ################## Family(ANSI) Family(DIN)

################## Component ################## Database Name: Master Database Family Group: Misc Digital Family: TIL Name: NAND2 Author: JG Date: March 11, 1998 Function: Thermal resistance junction: 0.00 Thermal resistance case: 0.00 Power dissipation: 0.00 Derating Knee Point: 0.00 Min Operating Temp: 0.00 Max Operating Temp: 0.00 ESD: 0.00 ################## Model ################## Model ID: NAND2 Model manufacturer: IIT Model template: a%p [%tA?%t:d%t;A + %tB?%t:d%t;B] + %tY?%t:d%t;Y %m Model data: .MODEL NAND2 d_nand ( rise_delay = 1n fall_delay = 1n) Model copyright: *********************************************** *ELECTRONICS WORKBENCH MODEL FILE * *MODELS GENERATED BY: * *(c) 1996 INTERACTIVE IMAGE TECHNOLOGIES LTD. * *TORONTO, ONTARIO (416)977-5550. * *********************************************** Военное)

Примечание. S –Schottky TTL (TTL схемы с транзистором Шоттки), LS – Low power Schotky TTL(маломощные), AS – Advanced Schottky TTL (улучшенные), ALS – улучшенные маломощные, F – Fast TTL (быстрые TTL, разработка фирмы Fairchild), H – High Speed – быстродействующие, L – Low Power (маломощные TTL).

Группа CMOS (цифровые схемы на комплементарных МОП - транзисторах) включает следующие серии: – CMOS_5v (10v, 15v), – 74HC_2v (4v, 6v), – Tinylogic_2v (3v, … 6v). Серии CMOS на сегодняшний день являются устаревшими и в практической разработке схем не используются, характеристики КМОП для 74-серий приведены в таблице. ИС технологии КМОП для 74-серий.

Примечание. MOS – (Metal Oxide Semiconductor), C – CMOS (complementary MOS), H – high (высокий), A – (advanced (усовершенствованный), Т – совместимый с TTL – уровнями, VH – Very High Speed (повышенное быстродействие), FCT – фирма Fairchild (сверхбыстродействующая совместимая с TTL), FCT-T – улучшенная по совместимости с TTL Размещение компонентов Процесс ввода схемы в рабочее окно программы Multisim начинается с размещения компонентов из библиотеки программы в соответствие с подготовленным эскизом (рис. 14). 1. Размещение логических компонентов из группы TTL. Вызовем браузер размещения и произведём выбор (рис. 15,а): группа TTL, серия 74STD, компонент 7408N (2 Input AND). Нажмём на кнопку ОК, что приведёт к появлению транспаранта с перечнем секций данного компонента, из которого выберем первую («А»). После этого на кончике курсору вы увидите изображение секции компонента (логического конъюнктора), установите курсор в нужном месте рабочего поля и щёлкните ЛКМ. Всё, одна секция установлена. Однако это снова приведёт к появлению транспаранта с перечнем секций компонента. Повторим вышеуказанные действия по установке следующей секции с обозначением «В» (рис. 15,б). Поскольку необходимости в использовании других секций данного компонента для схемы мультиплексора больше нет, нажмём на копку Cancel.

Рис. 15. Процедура использования браузера базы данных для выбора и размещения секций компонента 7408N. Заметим здесь, что данная особенность размещения секций компонента определена опцией Continuous placement for multi- section part only на закладке Parts диалогового окна Preferences, вызываемого командой Options/ Global Preferences! Если вам это процедура не нравится – снимите действие этой опции. Далее последовательно разместим из этой же серии по одной секции из компонентов 7432N(2 Input OR) и 7404 (Inverter). Рис. 16. Компоненты схемы для исследования MUX (2->1)

2.Размещение компонентов схемы формирования двоичных сигналов и устроойств визуальной регистрации (см. материал П. 9) Выберем 3 двухпозиционных интерактивных ключа Switch (расположение: Basic/Switch/Spdt), виртуальный элемент PullUp как источник H-уровня (расположение: Basic/Basic_Virtual/Variable_PullUp_Virtual), символ земли (Ground) как источник L-уровня. Для контроля за работой мультиплексора MUX (2->1) воспользуемся виртуальным логическим пробником Probe_ Dig_ Red из группы Indicators/Probe/Probe_Dig_Red. На рис. 16 показано рабочее окно ввода схемы с размещёнными компонентами. Прежде чем перейти к выполнению соединений компонентов проводниками необходимо произвести зеркальное отображение двухпозиционных интерактивных ключей в горизонтальной плоскости с помощью команды Edit/Flip Horizontal. Теричная цифра |

Код 8-4-2-1 | 7-сегментный выход | |||||||||||||||||||||||||||||||||||||||||||||

| 7 6 5 4 - 3 2 1 0 | |||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0000 | 0 0 1 1 - 1 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0001 | 0 0 0 0 - 0 1 1 0 | |||||||||||||||||||||||||||||||||||||||||||||

| 2 | 0010 | 0 1 0 1 - 1 0 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 3 | 0011 | 0 1 0 0 - 1 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 4 | 0100 | 0 1 1 0 - 0 1 1 0 | |||||||||||||||||||||||||||||||||||||||||||||

| 5 | 0101 | 0 1 1 0 – 1 1 0 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 6 | 0110 | 0 1 1 1 – 1 1 0 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 7 | 0111 | 0 0 0 0 – 0 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 8 | 1000 | 0 1 1 1 – 1 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| 9 | 1001 | 0 1 1 0 – 1 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| A | 1010 | 0 1 1 1 – 0 1 1 1 | |||||||||||||||||||||||||||||||||||||||||||||

| b | 1011 | 0 1 1 1 – 1 1 0 0 | |||||||||||||||||||||||||||||||||||||||||||||

| С | 1100 | 0 0 1 1 – 1 0 0 1 | |||||||||||||||||||||||||||||||||||||||||||||

| D | 1101 | 0 1 0 1 – 1 1 1 0 | |||||||||||||||||||||||||||||||||||||||||||||

| E | 1110 | 0 1 1 1 – 1 0 0 1 | |||||||||||||||||||||||||||||||||||||||||||||

| F | 1111 | 0 1 1 1 – 0 0 0 1 |

2. Автоматический режим. Например, создадим нужную нам возрастающую двоичную последовательность для демонстрации работы схемы. Нажмём на кнопку Set. Откроется ДО Settings (рис.19), в котором выберем опцию Up Counter и нажмём кнопку Accept.

Другие виды автоматического набора кодовых последовательностей изложены в сноске[1] к рис. 19.

Далее сообщим генератору XWG1 где находятся начальная (комбинация 0000=0h) и конечная ячейки (1111= 0Fh) памяти среди установленных 0400h ячеек. Дело в том, что моделирование начинается с генерирования начальной комбинации и заканчивается - конечной. Для этого на панели Word Generator XWG1 установим курсор на последовательность 0000 0000h (0h – для задействованных каналов), выделим её щелчком ЛКМ и вызвав всплывающее меню выполним команду Set Cursor, далее найдём комбинацию 0000 000Fh (Fh - для задействованных каналов), выделим её и выполним для неё команду Set Final Position. Обратите внимание на индикаторы (стилизованные стрелки¤£), отражающие начальную и конечную комбинации генерируемых комбинаций.

Запрограммировав Word Generator, надо выбрать режим его работы. Режим Cycle (Цикл) обозначает, что генератор будет циклически выводить запрограммированную последовательность, пока не будет остановлено моделирование. В режиме Burst (пакет) цикл будет выполнен один раз. В режиме Step (шаг) будет выведено содержимое одной ячейки, после чего моделирование будет остановлено (пошаговой режим). Если в процессе программирования генератора, щёлкнуть по ячейки правой кнопкой мыши установит опцию Set Breakpoint, то данная ячейка будет настроена как точка прерывания. Word Generator остановится в этой точке в режимах Cycle и Burst. Для удаления точки прерывания выполните опцию Delete Breakpoint. Во время моделирования курсор u в окне Word Generator - XWG1 указывает на текущую ячейку.

Запрограммировав Word Generator, надо выбрать режим его работы. Режим Cycle (Цикл) обозначает, что генератор будет циклически выводить запрограммированную последовательность, пока не будет остановлено моделирование. В режиме Burst (пакет) цикл будет выполнен один раз. В режиме Step (шаг) будет выведено содержимое одной ячейки, после чего моделирование будет остановлено (пошаговой режим). Если в процессе программирования генератора, щёлкнуть по ячейки правой кнопкой мыши установит опцию Set Breakpoint, то данная ячейка будет настроена как точка прерывания. Word Generator остановится в этой точке в режимах Cycle и Burst. Для удаления точки прерывания выполните опцию Delete Breakpoint. Во время моделирования курсор u в окне Word Generator - XWG1 указывает на текущую ячейку.

Процесс моделирования включает следующие шаги:

1. Курсором выделим начальную комбинацию и установим опцию Set Cursor

2. Выбрать кнопку с режимом моделирования (Cycle, Burst, Step) и щёлкнуть по ней мышью.

Реализация П.2 автоматически установит переключатель Simulation Switch (рис. 11) в режим моделирования, пока не окончится генерация слов, предусмотренная выбранным вами режимом моделирования. По окончанию режима моделирования (кроме режима Cycle) переключатель Simulation Switch установится в состояние Pause. Для продолжения моделирования снова щёлкните по соответствующей кнопке в окне Word Generator- XWG1. Остановить циклический режим моделирования можно только переключателем Simulation Switch, установив его в исходное состояние.

В заключение рассмотри другие органы управления устройства Word Generator, не востребованные в ходе данной демонстрации.

1. Частота посылок слов в циклическом и пакетном режимах устанавливается с помощью кнопок в окне Frequency.

2. Асинхронное управление цифрового устройства с квитированием. Сигнал Data Ready на клемме «R» сопровождает каждую выдаваемую на выход генератором слова кодовую комбинацию и используется в том случае, когда исследуемое устройство обладает свойством квитирования (подтверждения). В этом случае после получения очередной кодовой комбинации и сопровождающего его сигнала Data Ready, исследуемое устройство должно выдать сигнал подтверждения получения данных, который подается на вход синхронизации генератора слова (клемма «Т» - Trigger) и производит очередной его запуск. Сигнал Data Ready с клеммы «R» может быть использован и как обычный синхронизирующий сигнал в системах без квитирования (будет рассмотрено в следующем параграфе).

Битного сумматора .

В данном параграфе будет рассмотрена последовательность действий по разработке комбинационной схемы 4-битного сумматора, включающей её логическое тестирование программой Multisim.

1. Синтез схемы сумматора в заданном логическом базисе.

2. Понятие об иерархическом проектировании электронных схем. Создание подсхем.

3. Ввод материалов синтеза схемы в рабочие окна программы Multisim:

а) ввод материала по синтезу схемы сумматора в окно Description Box Editor,

б) ввод схемы сумматора в рабочее окно Circuit программы Multisim с учётом использования шин и подсхем.

4. Функциональное моделирование (логическое тестирование) схемы

Рис. SM- 2. Схема полусумматора HS в базисе И-НЕ/И-НЕ.

Построим одноразрядный сумматор SM, используя два полусумматора. На рис. SM-3 приведена таблица истинности SM. Поскольку полусумматор в качестве основной операции использует операцию сложения по mod2, то и логические уравнения для выходов SM должны быть выражены с использованием этой операции.

, (4)

, (4)

. (5)

. (5)

Рис. SM- 3. Таблица истинности одноразрядного SM и уравнения его работы.

Схема сумматора SM по уравнениям (4) и (5) представлена на рис SM-4.

Рис. SM- 4. Схема одноразрядного сумматора на основе полусумматора.

Многоразрядный сумматор с последовательным переносом.

На рис. SM-5 представлена схема многоразрядного сумматора с последовательным переносом для реализации

S=A+B, где

.

.

Рис. SM -5. Схема 4-битного сумматора на основе использования одноразрядных сумматоров

Время сложения в нём определится распространением переноса от самого младшего разряда к самому старшему (наихудший случай). Чем больше разрядность n сумматора, тем больше время суммирования. Это существенный недостаток, поэтому такая схема применяется при n ≤ 4

Создание подсхем.

Все современные программы моделирования электронных схем поддерживают иерархическое проектирования, основная идея которого состоит в том, что целый фрагмент схемы можно поместить в «чёрный ящик», отобразив его в виде специфического УГО с соответствующими входами и выходами. Использование таких УГО для повторяющихся фрагментов схемы моделирования, значительно упрощает не только её набор (ввод), но и позволяет схему структурировать до уровня описания, принятого в учебных пособиях. В программе моделирования Multisim 10.1 такие «чёрные ящики» реализуются как в виде иерархических блоков, так и подсхем. Создание иерархического блока, в отличие от подсхемы, оформляется в виде автономного файла, поэтому иерархические блоки могут использоваться только в составе проекта, включающего некоторую совокупность файлов моделирования. Пример разработки проекта моделирования цифровой схемы будет рассмотрено в заключительной части данной рукописи.

Подсхема не требует «файлового» оформления и может использоваться как составная часть обычного файла моделирования. Как иерархический блок, так и подсхема могут создаваться как «сверху - вниз» (сначала создаём УГО блока или подсхемы, а затем его (её) схему замещения), так и «снизу - вверх» (создаётся схема замещения, которая далее оформляется как иерархический блок или подсхема). Чтобы продемонстрировать оба способа примем следующий порядок действий. Подсхему полусумматора (рис. sm-2) создадим способом «сверху – вниз», а схему сумматора (рис. sm-4) на основе использования полусумматора (т.е. подсхемы полусумматора) – «снизу – верх».

Пример 3. Временное моделирование

(или исследование времени задержки переключения JK триггера).

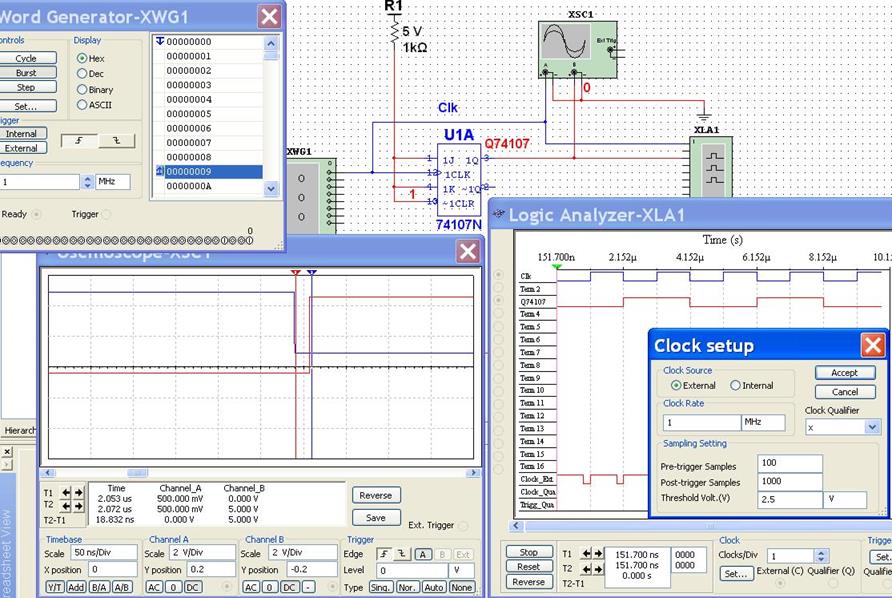

На рис. 42 приведена достаточно простая схема включения синхронного динамического JK-триггера (компонент 74107 N) в режиме Т-триггера (J=K=1), который будет каждый раз переключаться в новое состояние по срезу синхросигнала Clk.

Параметры временного моделирования JK-триггера:

1. Генератор слова Word Generator XWG1:

– Частота смены двоичных комбинаций 1 МГц (время выдачи одной комбинации 1мкс, период следования меандра синхросигнала Clk, образованного следованием двух комбинаций -2 мкс)

– Число установленных комбинаций -10, что соответствует 5 периодам синхросигнала Clk.

2. Логический анализатор Logic Analyser XLA1:

– Режим внешней синхронизации сигналом Data Ready Word Generator XWG1 c частотой 1 МГц.

– Масштаб временной развёртки Timebase Scale: 50 ns/Div,

– Канал 1. Положительное смещение 0,2 v, масштаб амплитудной развёртки 2 v/ Div

– Канал 2. Отрицательное смещение 0,2 v, масштаб амплитудной развёртки 2 v/ Div

Анализ временных диаграмм процесса переключения триггера на логическом анализаторе XLA1 показывает правильность его функционирование как Т-триггера. При этом частота переключения триггера (разность 2-х временных курсоров Т2-Т1=4 мкс) в 2 раза меньше частоты синхросигнала Clk. Однако на основании данных диаграмм мы ничего не можем сказать о задержки переключения триггера относительно среза синхросигнала.

Анализ временных диаграмм процесса переключения триггера на двулучевом осциллографе XSC1 позволяет это не только увидеть, но и замерить. На экране осциллографа отображён момент переключения триггера (красный цвет линии) из состояния 0 в 1 под действием среза синхросигнала Clk (синий цвет линии). Время задержки, зафиксированное разностью положения 2-х временных курсоров Т2-Т1, составляет ≈18,8 нс.

Рис. 42. Исследование задержки переключения JK-триггера

Пример 4. Создание проекта моделирования канала передачи данных с контролем по mod 2.

Постановка задачи.

Простейший способ обнаружения ошибок при передаче данных заключается в передаче разряда проверки на чётность P. (рис. 45). В контрольный разряд (КР) чётности записывается «0», если число единиц в информационном слове чётное и, наоборот - в случае нечётного числа. Достигается это применением схемы свёртки по mod 2. При этом общее количество передаваемых единиц по каналу связи, включая КР, всегда будет чётным. На принимающей стороне КР вычисляется тем же способом для информационных разрядов и сравнивается с переданным КР. При несовпадении фиксируется ошибка передачи. Исправить ошибку, к сожалению, невозможно, - надо использовать более сложные способы помехоустойчивого кодирования данных.

Ноябрь, 2009 г.

[1] Шаблоны настроек Preset Patterns:

Load – загрузить кодовые комбинации из файла с расширением .DP

Save – сохранить набор кодовых комбинаций в файле с расширением .DP

Clear buffer – очистить содержимое всех ячеек

Up counter – возрастающая последовательность чисел от 0 (начальная комбинация) до 3FFh (конечная)

Down counter- убывающая последовательность чисел от 400h (начальная комбинация) до 1 (конечная)

Shift right –бегущая 1 с позиции старшего канала в младший.

Shift left- бегущая 1 с позиции младшего канала в старший.

[2] Соответствие временных единиц измерения: 1с 1 1s, 1мс 1 1ms (m), 1 мкс 1 1 us (u или μ), 1нс 1 1 ns (n)

[3] Шина или линия групповой связи – это физическая среда передачи сигналов, к которой может параллельно подключаться несколько компонентов схемы.

MultiSim 10.1: – быстрый старт

Содержание

1. Введение

2. Настройка программы MultiSim 10.1 для моделирования цифровых схем.

2.1. Главное окно программы

2.2. Установка главных преференций для проектов в Multisim

2.3. Характеристики проекта для вновь открываемой схемы.

3. Структура элементной базы Multisim 10.1. Браузер размещения компонентов.

4. Виртуальные и реальные компоненты в базе данных Multisim10.1.

5. Характеристика групп цифровых компонентов TTL - и CMOS –логики.

6. Виды цифрового моделирования в Multisim 10.1.

7. Размещение символов “земли” и источников питания. Режимы моделирования

8. Проводники и точки соединения.

9. Простейший формирователь двоичных сигналов на основе интерактивного ключа

10. Пример 1. Функционального моделирование мультиплексора MUX (2->1))

10.1. Технология подготовки схемы

10.2. Размещение компонентов схемы MUX (2->1)) и формирователей двоичных сигналов

10.3. «Разводка» схемы и ввод пояснительных надписей

10.4. Моделированию схемы мультиплексора MUX (2->1))

11. Формирователи и регистраторы двоичных сигналов универсального типа.

11.1. Генератор слова XWG и семисегментный индикатор 16-теричных символов DCD_Hex

11.2. Регистрация работы генератора слова XWG логическим анализатором XLA.

12. Пример 2. Функциональное моделирование комбинационной схемы 4-битного сумматора.

12.1. Синтез схемы сумматора в заданном логическом базисе

12.2. Понятие об иерархическом проектировании электронных схем. Создание подсхем.

12.2.1. Создание подсхемы полусумматора HS способом «сверху - вниз».

12.2.2. Создание подсхемы одноразрядного сумматора SM способом «снизу - вверх».

12.3. Создание схемы моделирования 4-х битного сумматора с последовательным переносом. Использование шинной организации схемы.

12.4. Проверка правил электрического проектирования схемы сумматора.

12.5. Функциональное моделирование (логическое тестирование) схемы.

12.6. Спецификация схемы сумматора.

13. Проверка правильности выполнения электрической соединений в проектах программы Multisim 10.1

14. Пример 3. Временное моделирование

(или исследование времени задержки переключения JK триггера).

15. Графический самописец (дисплей) Grapher

16. Пример 4. Создание проекта моделирования канала передачи данных с контролем по mod 2.

16.1. Постановка задачи

16.2. Особенности реализации проекта в программе Multisim 10.1

16.3. Создание проекта моделирования.

■ Открытие проекта.

■ Открытие файла моделирования и отображение его в менеджере проекта.

■ Создание иерархического блока для схемы свёртки по mod 2.

■ Коррекция структуры менеджера проекта.

■ Создание схемы замещения иерархического блока.

■ Построение схемы моделирования канала передачи данных с контролем по mod 2.

■ Функциональное моделирование канала передачи данных.

Введение

Разработка любого цифрового устройства сопровождается физическим или математическим моделированием. Физическое моделирование связано с большими материальными затратами, поскольку требуется изготовление макетов и их трудоемкое исследование. Часто физическое моделирование просто невозможно из-за чрезвычайной сложности устройства, например, при разработке больших и сверхбольших интегральных микросхем. В этом случае прибегают к математическому моделированию с использованием компьютерных программ. В настоящее время разработано много подобных программ, использующих в качестве системного ядра программу SPICE -Simulation Program for Integrated Circuits Emphases (программа моделирования с ориентацией на интегральные схемы - разработка учёных университета Беркли, США), либо модели цифровых устройств на основе языков HDL (Hardware Description Languages) низкого (Altera HDL) и высокого уровней (VHDL –Very high speed integrated circuits HDL).

Составленные на входном языке Spice, математические модели компонентов схемотехнических устройств с высокой степенью достоверности соответствуют реальным элементам и используются в ряде подобных программ моделирования, так, например, HSpice (фирма MetaSoftware), PSpice (фирма MicroSim), Dr.Spice и ViewSpice (фирма Deutsch Research), Micro-Cap (фирма Spectrum Software), Spice3F5 и XSpice (фирмы National Instruments, сегодняшнего собственника программного продукта MultiSim 10.1).

MultiSim 10.1 представляет пакет программ для моделирования электронных схем и, при необходимости, последующей разводки печатных плат. Наследник знаменитого (особенно в академической среде) Electronics Workbench 5.12 от того же разработчика. Новые версии продуктов дополнены новыми средствами профессиональной разработки, в том числе инструментами моделирования, расширенной и улучшенной базой элементов, а также средствами совместной работы над проектом. Пользователь программы MultiSim не должен быть экспертом по программам SPICE, так как пользуется интуитивно понятной средой имитационного моделирования, гарантирующего высокое качество имитаций.

2. Настройка программы MultiSim 10.1 для моделирования цифровых схем.

Главное окно программы

Запустив программу и дождавшись её полной загрузки, вы увидите окно, отображённое на рис 1 (здесь красным цветом выделены главные части окна):

1. Главное меню программы (содержит команды для всех функций программы).

2. Стандартная панель, включающая общеупотребительные иконки в прикладных Windows-программах (View/Toolbars/Standard).

3. Панель управления Main (View/Toolbars/Main). Данная панель содержит кнопки для общих (основных) функций программы Multisim, а также окно In Use List, в котором содержится список всех компонентов, используемых в проекте.

4. Панель библиотек компонентов(View/Toolbars/Components).

5. Ключ симуляции (View/Toolbars/Simulation Switch), реализующий все режимы моделирования.

6. Панель (менеджер) проекта (View/Design Toolbox). Показывает иерархическую структуру схем и проектов.

7. Рабочая область ввода схемы (*Circuit) для симуляции вместе с панелью приборов (Instruments), использующихся как для задания входных сигналов, так и визуализации результатов симуляции.

8. Электронная таблица просмотра (Spreadsheet View) и редактирования параметров схемных компонентов и их обозначений (RefDes), а также просмотра результатов моделирования

Рис. 1. Окно программы MultiSim 10.1

Для того, чтобы окно программы выглядело как на рис. 1, выполните команду меню View/Toolbars и установите опции, указанные на рис. 2.

Рис. 2. Опции команды View/Toolbars, определяющие вид окна программы Multisim 10.1 на рис.1.

Последнее изменение этой страницы: 2019-03-21; Просмотров: 1543; Нарушение авторского права страницы