|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

Т а б л и ц а 2.3.1 Графические эквиваленты ФАЛ типовых элементов

Для синтеза схемы логического устройства элементы, реализующие логические операции, необходимо располагать от входа к выходу согласно их месту в заданной ФАЛ. Пример 2.3.10. Синтезировать схему для ФАЛ

ПРИМЕР СИНТЕЗА КОМБИНАЦИОННОГО ЛОГИЧЕСКОГО УСТРОЙСТВА В БАЗИСЕ 3И-НЕ Рассмотрим выполнение задания со следующими параметрами: вар. 1 (табл. 2.6), вар. 3 (табл. 2.7), вар. 6 (табл. 2.8). Согласно заданию из таблиц 2.6, 2.7 и 2.8 выбираем: · последовательность конституент единицы: 0, 3, 4, 6, 11, 12, 13, 14, · базис логических элементов: 3И-НЕ, · последовательность проверочных кодов: 0, 7, 3, 11, 2, 14, 9, 15, 8, 6. 1. По заданным конституентам единицы составим таблицу истинности. Так как максимальная из заданных конституент равна 14, то для отображения входного кода проектируемого устройства достаточно четырех входных переменных (четырехразрядного входного кода). Т а б л и ц а 2.4.1. Таблица истинности работы устройства

2. Используя составленную таблицу истинности, запишем СДНФ и CКНФ синтезируемого устройства. СДНФ:

СКНФ:

3. Минимальную дизъюнктивную форму ФАЛ получим с использованием карты Вейча. На карте Вейча (см. рис. 2.4.1) можно выделить 4 области, охватывающие все единичные значения функции. Первая область состоит из четырех элементов, описываемая произведением неизменных переменных Вторая область – из двух элементов, описываемая произведением неизменных переменных

Третья область – из двух элементов, описываемая произведением неизменных переменных Четвертая область – из двух элементов, описываемая произведением неизменных переменных Окончательно получим минимизированную ФАЛ вида

4. Приведем полученную ФАЛ к базису элементов 3И-НЕ:

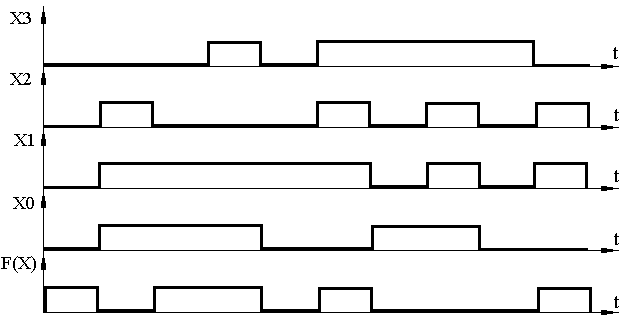

Следует отметить, что последний член выражения 5. По полученному выражению синтезируем схему логического устройства в заданном базисе 3И-НЕ (рис. 2.4.2). Для этого элементы, реализующие операцию функции Шеффера, располагают от входа к выходу согласно их месту в ФАЛ. Для получения сигналов, инверсных входным ( 6. Для получения временных диаграмм коды, заданные в таблице 7.8, последовательно подаются на входы спроектированного устройства и прослеживается сигнал, проходящий по всем элементам схемы. Эту проверку можно выполнить либо вручную, подставляя значения заданных переменных на входы устройства, либо с помощью соответствующего программного обеспечения, например, программы Multisim, используемой при выполнении лабораторных работ.

На рис. 2.4.3. приведены полученные в результате проверки временные диаграммы, поясняющие работу спроектированного устройства. Выводы по заданию 3.2

7. Выводы по заданию 2 должны содержать основные результаты, полученные при выполнении работы. Например: «В результате выполнения задания получены ФАЛ, формально описывающие заданный алгоритм функционирования устройства. Выполнена минимизация СДНФ, в результате которой найдена минимальная дизъюнктивная формы (МДНФ) записи ФАЛ. Минимизация выполнена с использованием карт Вейча. МДНФ ФАЛ приведена к виду, предполагающему ее реализацию на элементах 3И-НЕ. Синтезирована схема устройства в заданном базисе логических элементов, и, с использованием заданных проверочных кодов, проверена правильность ее функционирования. Результат проверки свидетельствует, что функционирование разработанной схемы соответствует исходному заданию». Задание 2.3 Популярное:

|

Последнее изменение этой страницы: 2016-06-05; Просмотров: 1345; Нарушение авторского права страницы