|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

|

Архитектура Аудит Военная наука Иностранные языки Медицина Металлургия Метрология Образование Политология Производство Психология Стандартизация Технологии |

АНАЛИЗ И СИНТЕЗ ТИПОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВСтр 1 из 9Следующая ⇒

Курсовая работа КР2 АНАЛИЗ И СИНТЕЗ ТИПОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ (ЗАДАНИЯ И МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ВЫПОЛНЕНИЮ КУРСОВОЙ РАБОТЫ КР2) Методические указания к выполнению курсовой работы КР2 «Анализ и синтез типовых электронных устройств» предназначены для студентов вузов, изучающих базовую дисциплину «Электротехника и электроника» в объёме 7-8 зачётных единиц (252-288 академических часов), включенной в примерные образовательные программы ФГОС ВПО-3 естественнонаучных профилей подготовки бакалавров и дипломированных специалистов. В методических указаниях излагается содержание курсовой работы КР2 по дисциплине «Электротехника и электроника» (модуль 2 «Электроника»), приводится перечень и варианты заданий, подлежащие выполнению, рекомендации по оформлению отчета по работе, основные теоретические положения, относящиеся к тематике заданий курсовой работы, и примеры выполнения заданий. Ц е л ь ю курсовой работы является: · получение навыков анализа и синтеза электронных устройств; · закрепление теоретических положений, рассмотренных на лекциях. Курсовая работа КР2 состоит из трёх заданий: З а д а н и е 2.1. Построение логарифмической амплитудно-частотной характеристики (ЛАЧХ) преобразователя сигналов на операционном усилителе (срок сдачи – в конце второго месяца семестра). З а д а н и e 2.2. Синтез комбинационного логического устройства в заданном базисе логических элементов (срок сдачи – в конце третьего месяца семестра). З а д а н и е 2.3. Синтез цифрового автомата (срок сдачи и защита курсовой работы – в зачётную неделю семестра). Итоговая оценка (отлично, хорошо, удовлетворительно, неудовлетворительно) за выполненную, оформленную в соответствии с требованиями к отчету по работе, и защищённую (в комиссии, состоящей обычно из двух преподавателей) курсовую работу заносится в зачётную ведомость учебной части института (деканата) в конце семестра. Студент, не выполнивший и не защитивший в текущем семестре курсовую работу или получивший неудовлетворительную оценку при ее защите (как и не выполнивший в полном объеме лабораторный практикум по модулю «Электроника»), к экзамену по дисциплине «Электротехника и электроника» не допускается кафедрой, о чем в соответствующей строке экзаменационной ведомости (напротив фамилии студента) в день экзамена ставится отметка н/к (не допущен к экзамену кафедрой). Отчет по курсовой работе оформляется на стандартных листах белой бумаги форматом А4, сброшюрованных в папку, на одной стороне листов с полями не менее 25-30 мм, где первая страница обложки может служить титульным листом отчета по работе. В верхней части обложки последовательно указать: Министерство образования и науки Российской Федерации ФГБОУ ВПО «МАТИ – Российский государственный технологический университет имени К. Э. Циолковского» (МАТИ) Кафедра «Прикладная математика, информационные технологии и электротехника» Ниже (по центру): Курсовая работа по модулю 2 «Электроника» базовой дисциплины для вузов «Электротехника и электроника» на тему: АНАЛИЗ И СИНТЕЗ ТИПОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ Ниже записать полный номер группы (например, 3ИНТ-2ДБ-202), фамилию И.О. студента, полный код расчётного варианта, например, КР2-13 – код 13-го варианта заданий курсовой работы КР2. Далее, привести данные: Выполнил(а): «___» __________201__г., Подпись студента. Сдано преподавателю на проверку «__»_ ____201__г., Проверил: __________ (доцент Иванов И. И.) «___» _______ 201__г. Внизу листа (по центру) записать имя города и текущий год. На следующей странице представляется Аннотация выполненной работы (не более 2/3 страницы) с краткой характеристикой расчётных схем устройств, используемых методов (законов, правил и т.п.) их анализа (синтеза) и полученных результатов выполнения заданий. Например, аннотация первого задания: «В Задании 2.1 проведен анализ частотных свойств преобразователя аналоговой информации, выполненном на основе операционного усилителя. При анализе схемы и её расчёте использован операторный метод получения передаточных функций элементарных звеньев и преобразователя, охваченного цепью отрицательной обратной связи. На основе передаточной функции рассчитана и построена ЛАЧХ заданного преобразователя и определены основные параметры устройства». Аналогично даётся аннотация выполненных 2-го и 3-го заданий работы КР2. На третьей странице пояснительной записки приводится полное задание на курсовую работу (см. стр. 2). На четвертой странице записывается заглавие задания 2.1 курсовой работы КР2 и под ним (в скобках) код расчётного варианта. Ниже вычерчивается (с соблюдением ГОСТ 2.721-74) принципиальная электрическая схема устройства и под ней записываются из таблицы 2.1 исходные данные для расчёта заданного варианта, например: DА - К140УД10, R1 = 36 кОм, R2 = 12 Ом, С1 =... и т.д. Далее, выполняется поэтапный расчёт схемы цепи с соответствующими заголовками каждого этапа (шага), с вычерчиванием необходимых расчётных схем с условно положительными направлениями токов и напряжений, с записью уравнений и формул в общем виде с последующей подстановкой численных значений входящих в формулы физических величин и с записью промежуточных результатов расчёта (для поиска возможных ошибок в расчёте преподавателем). Результаты расчётов следует округлять, оставляя не более четырех-пяти значащих цифр, выражая числа с плавающей запятой, если они велики или малы. Диаграммы и графики вычерчиваются на миллиметровой бумаге (или на листах с мелкой сеткой при выполнении работы на ПК) с использованием соответствующих равномерных или логарифмических масштабов по осям и с указанием размерностей. Рисунки и диаграммы должны быть пронумерованы и снабжены надписью, например, Рис. 2. ЛАЧХ последовательного звена коррекции. Нумерация, как рисунков, так и формул – сквозная по всем трём заданиям! Далее, продолжение оформления отчётов по 2-му и 3-му заданиям. По результатам расчётов и графических построений формулируются выводы по каждому заданию или в конце отчёта – по всей курсовой работе. На последней странице отчета студент ставит свою подпись и дату завершения выполнения работы. В н и м а н и е. 1. Небрежно оформленные отчеты по курсовой работе возвращаются студентам для переоформления. Также преподаватель возвращает отдельным студентам отчеты на доработку с пометками ошибок на листах или с перечнем замечаний и рекомендаций по исправлению ошибок на титульном листе. 2. После защиты курсовых работ, пояснительные записки студентов групп с отметкой и подписью преподавателя (двух преподавателей) на титульных листах, занесенных также в соответствующую ведомость и в зачётные книжки студентов, сдаются на кафедру для хранения в течение двух лет. Задание 2.1 РАСЧЕТ И ПОСТРОЕНИЕ ЛОГАРИФМИЧЕСКОЙ АМПЛИТУДНО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ ПРЕОБРАЗОВАТЕЛЯ СИГНАЛОВ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ Рис. 2.1. Обобщенная схема преобразователя аналоговых сигналов ПРИМЕР ПОСТРОЕНИЯ ЛАЧХ Выводы по заданию КР2-1 Исследуемый преобразователь аналоговых сигналов фактически является фильтром нижних частот, обеспечивающий передачу сигналов в диапазоне частот 0…w1, и ослабление сигналов на уровне -6, 14 дБ в диапазоне частот w2…w3. После частоты w3 ЛАЧХ имеет постоянный наклон -20 дБ/дек. Задание 2.2 БАЗИСЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ По заданным параметрам синтезировать схему комбинационного устройства в заданном базисе логических элементов. Для этого согласно варианту (см. табл. 2.5 и табл. 2.6) необходимо: 2.2.1. По исходным данным составить таблицу истинности устройства. 2.2. Записать совершенную дизъюнктивную (СДНФ) и совершенную конъюнктивную (CКНФ) функции алгебры логики (ФАЛ), описывающие поведение устройства. 2.2.3. Минимизировать ФАЛ устройства. 2.2.4. Привести минимизированную ФАЛ к базису заданных логических элементов (см. табл. 2.7). 2.2.5. Синтезировать схему устройства в заданном базисе логических элементов. 2.2.6. Нарисовать временные диаграммы, поясняющие работу синтезированного устройства при подаче на его вход заданной последовательности проверочных входных кодов (см. табл. 2.8). 2.2.7. Сформулировать выводы по результатам выполненного задания. Т а б л и ц а 2.5. Варианты задания 2.2 курсовой работы КР2

Решение. В результате имеем 3 элемента 2И-НЕ и один элемент 3И-НЕ. Пример 2.3.4. Привести ФАЛ к базису элементов ИЛИ-НЕ: В результате имеем 3 элемента 2ИЛИ-НЕ, один элемент 3ИЛИ-НЕ и один инвертор, который так же можно выполнить на элементе ИЛИ-НЕ. 2.3.6. Приведение ФАЛ к заданному числу входов логического элемента. Здесь возможно два случая: · число реальных входов логического элемента больше числа, требуемого ФАЛ, · число реальных входов логического элемента меньше числа, требуемого ФАЛ. В первом случае используются следующие формулы:

Пример 2.3.5. Привести ФАЛ

Пример 2.3.7. Преобразовать ФАЛ

Пример 2.3.8. Преобразовать ФАЛ

или Последнее преобразование менее предпочтительно, так как при реализации приводит к большим задержкам получения результата. Аналогично преобразуется число входов ФАЛ и элементов ИЛИ-НЕ. Пример 2.3.9. Преобразовать ФАЛ

2.3.7. Вычерчивание схемы устройства по его ФАЛ. Графические эквиваленты типовых элементов ФАЛ приведены в таблице 2.3.1. ПРИМЕР СИНТЕЗА КОМБИНАЦИОННОГО ЛОГИЧЕСКОГО УСТРОЙСТВА В БАЗИСЕ 3И-НЕ Рассмотрим выполнение задания со следующими параметрами: вар. 1 (табл. 2.6), вар. 3 (табл. 2.7), вар. 6 (табл. 2.8). Согласно заданию из таблиц 2.6, 2.7 и 2.8 выбираем: · последовательность конституент единицы: 0, 3, 4, 6, 11, 12, 13, 14, · базис логических элементов: 3И-НЕ, · последовательность проверочных кодов: 0, 7, 3, 11, 2, 14, 9, 15, 8, 6. 1. По заданным конституентам единицы составим таблицу истинности. Так как максимальная из заданных конституент равна 14, то для отображения входного кода проектируемого устройства достаточно четырех входных переменных (четырехразрядного входного кода). Т а б л и ц а 2.4.1. Таблица истинности работы устройства

2. Используя составленную таблицу истинности, запишем СДНФ и CКНФ синтезируемого устройства. СДНФ:

СКНФ:

3. Минимальную дизъюнктивную форму ФАЛ получим с использованием карты Вейча. На карте Вейча (см. рис. 2.4.1) можно выделить 4 области, охватывающие все единичные значения функции. Первая область состоит из четырех элементов, описываемая произведением неизменных переменных Вторая область – из двух элементов, описываемая произведением неизменных переменных

Третья область – из двух элементов, описываемая произведением неизменных переменных Четвертая область – из двух элементов, описываемая произведением неизменных переменных Окончательно получим минимизированную ФАЛ вида

4. Приведем полученную ФАЛ к базису элементов 3И-НЕ:

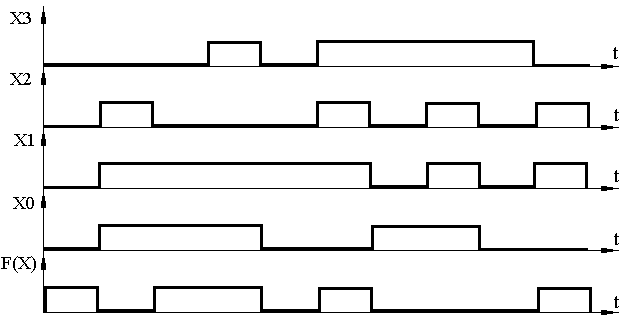

Следует отметить, что последний член выражения 5. По полученному выражению синтезируем схему логического устройства в заданном базисе 3И-НЕ (рис. 2.4.2). Для этого элементы, реализующие операцию функции Шеффера, располагают от входа к выходу согласно их месту в ФАЛ. Для получения сигналов, инверсных входным ( 6. Для получения временных диаграмм коды, заданные в таблице 7.8, последовательно подаются на входы спроектированного устройства и прослеживается сигнал, проходящий по всем элементам схемы. Эту проверку можно выполнить либо вручную, подставляя значения заданных переменных на входы устройства, либо с помощью соответствующего программного обеспечения, например, программы Multisim, используемой при выполнении лабораторных работ.

На рис. 2.4.3. приведены полученные в результате проверки временные диаграммы, поясняющие работу спроектированного устройства. Выводы по заданию 3.2

7. Выводы по заданию 2 должны содержать основные результаты, полученные при выполнении работы. Например: «В результате выполнения задания получены ФАЛ, формально описывающие заданный алгоритм функционирования устройства. Выполнена минимизация СДНФ, в результате которой найдена минимальная дизъюнктивная формы (МДНФ) записи ФАЛ. Минимизация выполнена с использованием карт Вейча. МДНФ ФАЛ приведена к виду, предполагающему ее реализацию на элементах 3И-НЕ. Синтезирована схема устройства в заданном базисе логических элементов, и, с использованием заданных проверочных кодов, проверена правильность ее функционирования. Результат проверки свидетельствует, что функционирование разработанной схемы соответствует исходному заданию». Задание 2.3 ЦИФРОВОГО УСТРОЙСТВА), РЕАЛИЗУЮЩЕГО ЗАДАННЫЙ АЛГОРИТМ ФУНКЦИОНИРОВАНИЯ По известным параметрам синтезировать схему последовательностного устройства, формирующего на выходе заданную последовательность двоично-десятичных кодов. Для этого согласно варианту (см. табл. 2.9) необходимо: 2.3.1. Определить число необходимых состояний и объем памяти цифрового автомата. 2.3.2. Преобразовать заданную последовательность выходных чисел к виду двоично-десятичного кода. 2.3.3. Определить разрядность выходного кода устройства. 2.3.4. Нарисовать обобщенную структурную схему проектируемого устройства. 2.3.5. Составить граф переходов цифрового автомата. 2.3.6. Выбрать тип триггера для реализации триггерной подсистемы цифрового автомата и записать его таблицу переходов. 2.3.7. Составить расширенную таблицу истинности, описывающую поведение проектируемого цифрового автомата. 2.3.8. Записать минимизированные ФАЛ, описывающие алгоритм работы комбинационной подсистемы устройства. 2.3.9. Привести полученные ФАЛ к стандартному базису логических элементов. 2.3.10. Составить схему цифрового автомата. 2.3.11. Нарисовать временные диаграммы, поясняющие работу разработанного устройства. 3.12. Сформулировать выводы по работе. Т а б л и ц а 7.9. Варианты задания 2.3 курсовой работы КР2

ЦИФРОВЫХ УСТРОЙСТВ 2.5.1 Основные определения. Последовательностными устройствами или автоматами с памятью называют логические устройства, выходной сигнал которых определяется не только действующей в настоящий момент на входе комбинацией переменных, но и всей последовательностью входных и выходных переменных, действовавших в предыдущие моменты времени.

Реализация такого алгоритма работы предполагает, что на входе некоторого логического устройства действует не только комбинация внешних входных сигналов, но и некоторые сигналы, отображающие предысторию работы устройства. Такие сигналы могут вырабатываться в самом комбинационном устройстве и совместно с внешними подаваться на его вход. Очевидно, что, по сути, в последовательностном устройстве существует канал передачи информации с его выхода на вход, причем эта информация суммируется с внешней. Следовательно, такой канал передачи является цепью положительной обратной связи (ПОС), охватывающей исходное комбинационное устройство. На рис. 2.5.1 приведена обобщенная структурная схема, реализующая описанный алгоритм работы устройства. Представленная на рис. 2.5.1 структура является конечным автоматом, известным как автомат Мили. Если в схеме отсутствует входной сигнал X[n-1…0], то получим структуру, известную как автомат Мура. В зависимости от выполнения блока ПОС, данная структура порождает два класса устройств. Если в качестве блока обратной связи используется комбинационное устройство, получаем класс устройств называемых триггерами. Эти устройства являются элементарными ячейками памяти, способными хранить один бит информации. Если блок обратной связи сам выполнен как последовательностное устройство, например триггер, то получаем более сложное устройство, которое и является конечным автоматом. Рассмотрим особенности работы обоих классов последовательностных устройств. 2.5.2. Триггеры. Триггером называется устройство, способное формировать два устойчивых значения выходного сигнала и скачкообразно изменять эти значения под действием внешнего управляющего сигнала. Простейший триггер может быть построен, если в качестве комбинационного логического устройства использовать простейший элемент 2И-НЕ или 2ИЛИ-НЕ. Так как эти элементы содержат инвертор, то для формирования сигнала ПОС выходной сигнал элемента необходимо дополнительно инвертировать. С этой целью можно использовать второй такой же элемент. На рис. 2.5.2 приведены два варианта построения простейшего триггера. Он снабжен двумя информационными входами: X1 и X0 и двумя выходами

Из таблиц следует, что существует три разновидности комбинаций входных сигналов Х1 и Х0. Первая - это комбинация, при которой значение выходного сигнала остается неизменным. Вторая – комбинация, которая однозначно определяет выходной сигнал устройства. И третья – это запрещенная комбинация, при которой не выполняется определение триггера (сигнал  ), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать. ), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать.

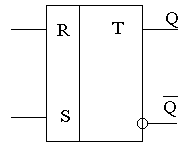

Реальные схемы триггеров содержат одну или несколько из приведенных ячеек памяти и некоторую комбинационную схему, предназначенную для формирования информационных сигналов Х1 и Х0. При описании поведения триггера пользуются понятиями: триггер установлен или триггер находится в состоянии установки – выходной сигнал Q = 1; триггер сброшен или триггер находится в сброшенном состоянии – выходной сигнал Q = 0, а так же понятием активного входного сигнала, под которым понимают такое его значение, которое однозначно определяет выходной сигнал устройства. Существующие типы триггеров можно квалифицировать по различным признакам. Наиболее часто в качестве такого признака используют тип информационных входов, управляющих работой триггера. Различают следующие типы управляющих входов триггеров: R – раздельный вход сброса триггера (Q = 0); S – раздельный вход установки триггера (Q = 1); K – вход сброса универсального триггера (Q = 0); J – вход установки универсального триггера (Q = 1); T – счетный вход триггера; D – информационный вход, сигнал которого переписывается на выход (Q = D); С – вход синхронизации. По этим признакам различают синхронные (переключаются только при наличии сигнала на входе синхронизации С) и асинхронные (переключаются сразу после изменения информационных сигналов) RS-, T-, JK- и D-триггеры, последние могут быть только синхронными. Простейшими триггерами (см. рис. 2.5.2) являются асинхронные RS-триггеры. Для триггера (рис. 2.5.2а) активным входным сигналом является сигнал «лог. 0». Вход Х1 = S, вход X0 = R. Для триггера (рис. 2.5.2б) активным является сигнал «лог. 1»: вход Х1 = R, X0 = S. Условное изображение асинхронного RS-триггера показано на рис. 2.5.3. В левом выделенном поле указываются все информационные входы триггера. При этом, если активным логическим сигналом является сигнал «лог. 0», то соответствующий вход снабжается кружком (как выход

На практике, работу триггера удобно описывать не таблицами истинности, а таблицами переходов, указывающими, какая комбинация информационных сигналов приводит к заданному изменению выходного сигнала (состояния) триггера. На практике, работу триггера удобно описывать не таблицами истинности, а таблицами переходов, указывающими, какая комбинация информационных сигналов приводит к заданному изменению выходного сигнала (состояния) триггера.

В табл. 2.5.1 приведены возможные схемы и таблицы переходов различных типов триггеров при условии, что активным логическим сигналом является сигнал «лог. 1». П р и м е ч а н и я. 1. Таблицы переходов приведены для случая асинхронных триггеров. Работу синхронного триггера можно описать следующей ФАЛ:

т.е. синхронный триггер переключается только в момент активного уровня сигнала на его входе синхронизации С. ПРИМЕР СИНТЕЗА ПОСЛЕДОВАТЕЛЬНОСТНОГО ЛОГИЧЕСКОГО УСТРОЙСТВА Рассмотрим пример синтеза последовательностного устройства, формирующего на выходе следующую последовательность кодов: 21, 97, 67, 21, 38, 96. Популярное:

|

Последнее изменение этой страницы: 2016-06-05; Просмотров: 1854; Нарушение авторского права страницы